Introduction

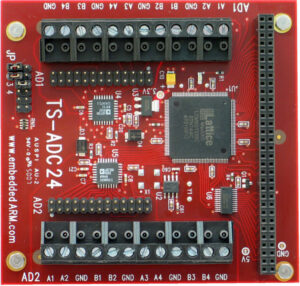

This is a developer’s note about rewriting the Application Programming Interface (API) for the TS-ADC16 and TS-ADC24 PC/104 peripherals. With the existing API being written in 2010 it was decided that a rewrite would be more effective than a comprehensive update. This article will cover the details of the development for the new API and also briefly describe the functions in the API.

Continue reading “Developer Notes on API Rewrite for TS-ADC16 and TS-ADC24”